接口宏

DDR接口

从低中速传输带宽到高速传输带宽和低功耗,本公司提供各种工艺的多样的DDR接口宏。另外,依托采用Chip-Package-Board协调设计的设计支持,我们也提供追求信号质量和成本优化的开发支持服务。

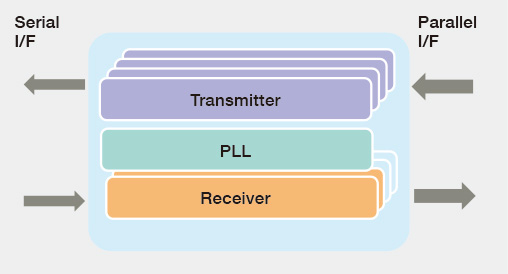

[DDR接口结构图]

![[DDR接口结构图]](images/interface_01.jpg)

DDR接口宏

高速/高带宽:DDR

低功耗:LPDDR

宽带:HBM

基于PHY功能(Training功能),与许多不同的DRAM配置和PKG选项兼容,如Fly-by、PoP和DIMM。

支持DDR接口设计(Chip-Package-Board协调设计)

时序验证:验证包括LSI I/O ~ DRAM间延迟的DDR-IF整个系列的时序

电源完整性:作为电源阻抗设计的一部分,优化寄生电感、共振频率和电源(PKG、PCB)阻抗

信号完整性:优化驱动器强度、终端电阻和互连网络拓扑结构

总线切换验证:优化了总线读写时序

![[LPDDR 8.5Gbps PoP]](images/interface_002.jpg)

MIPI接口

用于搭建与高速、高分辨率的CMOS图像传感器相连的相机及显示器系统的高速接口。提供可实现高度影像表现力的解决方案。

MIPI C/D-PHY宏

传输速度 C-PHY 3.5Gsps(8Gbps) @ 1lane

传输速度 D-PHY 4.5Gbps @ 1lane

C-PHY Rx接收容限测试波形

PCI Express接口

随着近些年CPU处理能力的飞跃性提高和对大容量数据传输需求的增加,以现有的总线实现用户期待的系统性能已变得非常困难。而Socionext使用的PCI Express接口的数据传输速率数高达数百兆字节,能够很好地解决此类问题。

PCI Express 评估环境

![[PCI Express 评估环境]](images/interface_07.jpg)

PCI Express 输出波形@32Gbps

![[PCI Express 输出波形@32Gbps]](images/interface_07_2.jpg)

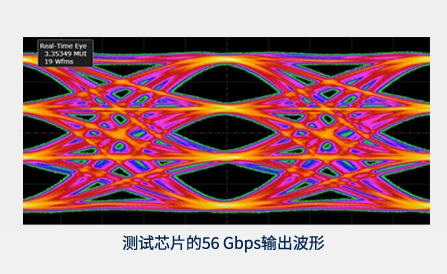

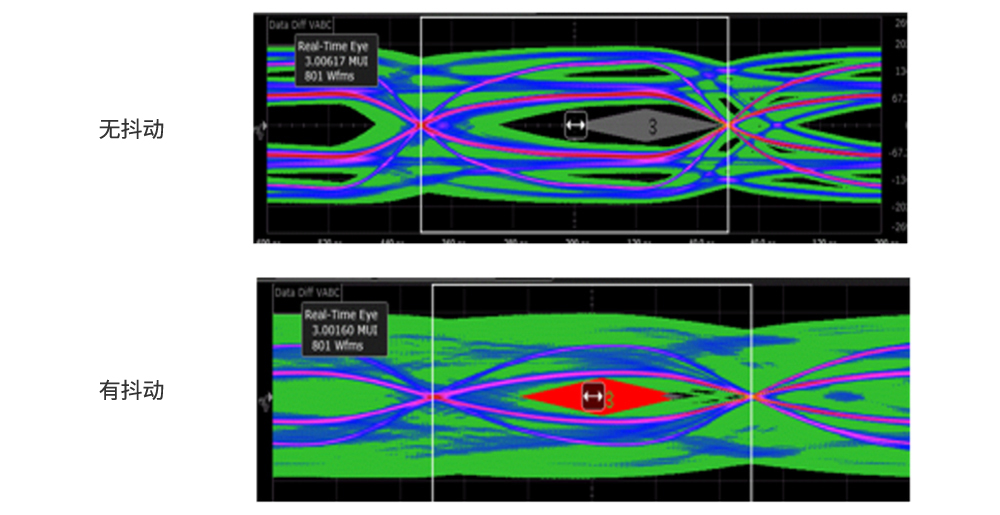

1G-56Gbps SerDes接口

每个通道具备1 Gbps至56.4 Gbps的传输性能,通过组成多个通道,本公司可以提供用于构建100G/200G/400G的光纤网络和100G 以太网系统的高性能SerDes宏。

通过内置低抖动的高性能PLL,可实现每个通道最大28 Gbps(PAM4 56Gbps)的强大的传输功能。支持OIF-CEI-11G-SR、OIF-CEI-28G-SR、OIF-CEI-28G-VSR、OIF-CEI-56G-VSR、IEEE802.3ba CAUI、IEEE802.3bm CAUI4和XFI等各种规格。