インタフェース・マクロ

DDRインタフェース

低中速転送帯域から高速転送帯域やLow Powerまで、さまざまなDDRインタフェース・マクロを各種テクノロジで提供可能です。また、Chip–Package–Boardの協調設計による設計支援で品質とコストの最適化を図る開発をサポートします。

[DDRインタフェース構成図]

![[DDRインタフェース構成図]](images/interface_01.jpg)

DDRインタフェース・マクロ

高速/高帯域(高速マクロ):DDR

Low Power(低消費電力マクロ):LPDDR

広帯域:HBM

PHY機能(Training機能)により、Fly-by, PoP,DIMMなどの多彩なDRAM配置、パッケージオプションに対応

DDRインタフェース設計サポート(Chip–Package–Board 協調設計)

Timing検証:LSI.I/OからDRAM間の遅延を含めたDDR- IF全系のTimingを検証

Power Integrity:電源 Impedance設計として寄生インダクタンス、共振周波数、電源(PKG, PCB)インピーダンスを最適化

Signal Integrity:Driver Strength、終端抵抗、配線Topologyの最適化

バス切替検証:Write/Readバス切替タイミングの最適化

![[LPDDR 8.5Gbps PoP設計]](images/interface_002.jpg)

MIPIインタフェース

高速・高解像度CMOSイメージセンサーとのカメラおよびディスプレイシステムを構築するための高速インタフェースです。高い映像表現力を実現するソリューションを提供可能です。

MIPI C/D-PHY マクロ

伝送速度 C-PHY 3.5Gsps(8Gbps) @ 1lane

伝送速度 D-PHY 4.5Gbps @ 1lane

C-PHY Rx 受信耐性試験波形

PCI Expressインタフェース

近年の飛躍的なCPU処理能力向上と大容量データ転送ニーズの拡大に伴い、既存バスでは期待するシステム性能を実現することが非常に難しくなっています。この課題を克服するために、数ギガバイトのデータ転送を可能とする高速インタフェースが、PCI Express技術です。

当社評価環境において、PCI Express 規格のコンプライアンステストをパスすることを確認済です。

PCI Express 評価環境

![[PCI Express 評価環境]](images/interface_07.jpg)

PCI Express 出力波形 @32Gbps

![[PCI Express 評価環境]](images/interface_07_2.jpg)

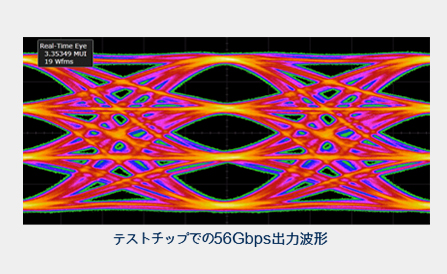

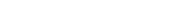

1G–56Gbps SerDesインタフェース

1レーン当たり1Gbps ~ 56.4Gbpsの伝送性能を有し、複数チャネル構成とすることにより、100G/200G/400Gの Optical networkや100G Etherシステムを構築するための高性能SerDesマクロを提供可能です。

低ジッタの高性能PLLを内蔵することにより、1レーン当 たり最大28Gbaud(PAM4 56Gbps)のロバストな伝送を可能としました。OIF-CEI-11G-SR, OIF-CEI-28G-SR, OIF-CEI-28G-VSR, OIF-CEI-56G-VSR, IEEE802.3ba CAUI, IEEE802.3bm CAUI4, XFIなどの様々な規格をサポート可能です。